# Scheduling Directives for Shared-Memory Many-Core Processor Systems Oded Green, Yitzhak Birk

CCIT Report #803 January 2012

# Scheduling Directives for Shared-Memory Many-Core Processor Systems

Oded Green, Yitzhak Birk

Electrical Engineering Department

Technion – Israel Inst. of Technology

Haifa 32000, Israel

# **Contents**

| Abstract | 5                                            |

|----------|----------------------------------------------|

| 1        | Introduction6                                |

| 1.1      | Many-core systems6                           |

| 1.2      | Shared-memory systems6                       |

| 1.3      | Existing many-core systems7                  |

| 1.3.1    | Graphic Processing Units                     |

| 1.3.2    | Tilera8                                      |

| 1.3.3    | XMT9                                         |

| 1.3.4    | Plurality10                                  |

| 1.4      | Shared-memory many-core system challenges    |

| 1.5      | Performance evaluation for many-core systems |

| 1.6      | Scheduling                                   |

| 1.7      | Online Vs. Offline scheduling17              |

| 1.8      | Overview17                                   |

| 2        | Fine grain parallelism for many-core systems |

| 2.1      | Introduction                                 |

| 2.2      | Workload breakdown                           |

| 2.3      | Forks and Joins                              |

| 2.4   | Duplicable Tasks                                           | 20         |

|-------|------------------------------------------------------------|------------|

| 2.5   | Expressive power limitations due to precedence constraints | 21         |

| 2.5.1 | Example of limited expressive power - regular tasks        | 21         |

| 2.5.2 | Example of limited expressive power - duplicable tasks     | <b>2</b> 3 |

| 2.6   | Duplicable-task scheduling                                 | 26         |

| 2.7   | Different levels of granularity for duplicable tasks       | 26         |

| 3     | Scheduling directives for regular tasks                    | 28         |

| 3.1   | Introduction                                               | 28         |

| 3.2   | Start After Start                                          | 28         |

| 3.2.1 | Motivation for Start After Start                           | 29         |

| 3.2.2 | Implementation of SAS directive                            | 30         |

| 3.3   | Regular tasks scheduling directives summary                | 32         |

| 4     | Scheduling directives for duplicable tasks                 | 33         |

| 4.1   | What are scheduling directive for duplicable tasks?        | 33         |

| 4.2   | Regular tasks are simply too much                          | 35         |

| 4.3   | Task fusion is not feasible                                | 35         |

| 4.4   | What sort of directives do we want?                        | 36         |

| 4.5   | Priority Primitive for Duplicable Tasks                    | 38         |

| 4.6   | Applicable directives for duplicable tasks                 | 39         |

| 4.6.1 | Start After Start for duplicable tasks                     | 39         |

| 4.6.2 | Limit Number of Active Replicas                            | 45         |

| 4.6.3 | Assign Cores Fairly                                        | 47         |

|   | 4.7         | Hardware-extending directives for duplicable tasks                                                                  | . 50 |

|---|-------------|---------------------------------------------------------------------------------------------------------------------|------|

|   | 4.7.1       | Supporting correctness for duplicable tasks                                                                         | . 50 |

|   | 4.7.2       | Logarithmic Re-Order Buffer for Duplicable Tasks                                                                    | . 52 |

|   | 4.7.3       | Start After Complete for duplicable tasks                                                                           | . 54 |

|   | 4.7.4       | Limit Number of Replicas after Earliest Active                                                                      | . 59 |

|   | 4.7.5       | Start After Merged Completion                                                                                       | . 61 |

|   | 5           | Scheduling decision: dispatch duplicable task or regular task                                                       | . 66 |

|   | 6           | Efficiency of cache use                                                                                             | . 73 |

|   | 7           | Conclusions and future work                                                                                         | . 76 |

| R | eferences   |                                                                                                                     | .78  |

| R | 5<br>6<br>7 | Scheduling decision: dispatch duplicable task or regular task  Efficiency of cache use  Conclusions and future work | . 7  |

#### **Abstract**

We consider a shared-memory (no private caches) many-core architecture. A program comprises a set of single-core tasks along with a set of precedence relations among them, which represent data dependences and ensure correct execution. For reasons such as programming convenience and reduced code foot print, multiple-instance ("duplicable") tasks are used in data-parallel situations such as summing up the rows of a matrix. Dispatching tasks to cores is done by hardware within very few clock cycles and at a very high rate. This is thus a dataflow machine at the inter-task level, with conventional control flow within each task. The Plurality Hypercore is such an architecture.

The precedence constraints guarantee correctness, and the absence of private caches obviates the need to consider which core should execute any given task. However, one must still decide the dispatching order whenever the number of runnable tasks exceeds that of available cores. This choice among correct execution orders can impact performance: 1) it can mitigate bottlenecks, namely situations wherein a task that must precede many others is scheduled later than it could have been and now causes cores to be idle awaiting its completion, and 2) it can impact the instantaneous memory footprint of the program and its data, thereby affecting the hit rate of the shared cache. For a given number of cores and a program with known task execution times, one could simply add precedence relations in order to enforce the desired scheduling order. This, however, is impossible in general, and the problem is most acute with duplicable tasks, as the precedence constraints apply jointly to all task instances.

This work focuses on scheduling constructs ("primitives") that can be used by programmers and by automatic optimization tools to further direct the runtime dispatcher, with special attention to duplicable tasks. Such constructs must express relations that occur in real programs and whose translation into scheduling directives impacts performance. Additionally, they must lend themselves to efficient implementation in hardware. We present several such primitives that increase the expressive power of the programmer and/or optimizer, along with examples in which they increase performance with different numbers of cores. We also outline their implementation in the context of a Hypercore-like system, thereby proving them to be practical.

#### 1 Introduction

# 1.1 Many-core systems

A single core system is a system that has one core that can execute programs. With the advance in technology, it has become possible to place multiple cores on a single chip/die or on multiple chips/dies and interconnecting them. Furthermore, from a power performance point of view, it has become less practical to increase the clock speed of single cores system due to the increase in power requirements. The term "many-core" is used to refer to cores whose efficient use requires the effective parallelization of an application rather than merely relying on the existence of a sufficient number of concurrently running independent applications. One should thus think of at least 16 cores.

# 1.2 Shared-memory systems

Shared memory refers to memory that will be accessed by several cores simultaneously. The shared memory is both physically and logically shared by the different cores. Logically, the address space is the same. Physically, the same hardware-memory is used by the different cores. There are two types of shared memory systems:

- NUMA Non Uniform Memory Access access time of a given core to different memory addresses in the same level of the memory hierarchy varies due to the fact that different parts of the memory are at different distances from that core.

- UMA –Uniform Memory Access access time to the entire same-level memory is equal.

Also, it is possible to have memory hierarchies such as:

- Private caches for the cores in this hierarchy it is possible to reduce the latency of memory requests by keeping data near the core. However, this approach suffers from the need for coherency-preserving mechanisms.

- Several layers of shared memory for example, a hierarchy with a shared cache for all the cores

and an additional (larger) shared memory that the shared caches goes to for cache misses. Note

that UMA/NUMA refers to same-level access times, and is thus "orthogonal" to the issue of a

multi-level hierarchy.

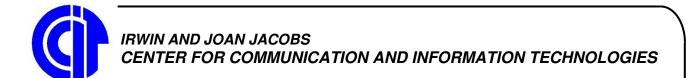

Figure 1 - A set of multi-cores with on-chip shared memory. Essentially this is the GPU .lmage taken from NVidia.

# 1.3 Existing many-core systems

Today there are numerous many-cores systems. A few of them will now be presented.

# 1.3.1 Graphic Processing Units

Graphic Processing Units (GPU) are systems that originally were created for high-speed rendering of complex graphics for display on computer screens. As graphical computation is intensive and inherently parallel, these systems were widened in such a way that they would be able to deal with multiple data elements concurrently. In recent years, following Moore's law, it has become possible to create even wider machines. Furthermore, it has become clearer that these machines can be used not only to speed up graphical algorithms, but, rather to speed up algorithms that are *data* parallel. In fact, the so called cores, known as processing elements(PE), of the GPU are actually clustered into groups of PE that share a program counter, pipe and control unit.

The following points present some of the key architectural highlights of the platform:

- All the PEs in the same control unit execute the same instruction in each cycle(share the same program counter)

- Control units can execute several threads concurrently.

- Memory architecture is NUMA. Each of the clusters has a shared cache.

- The GPU's scheduler is fast, efficient and keeps all the cores utilized when the workload is large enough.

- High memory bandwidth:

- On chip between PE's and GPU's main memory.

- o Between host(CPU) and GPU.

- Frequency of the systems is in the 500MHz 700MHz region.

- Power consumption of the GPU is considerably high and can reach several hundred Watts.

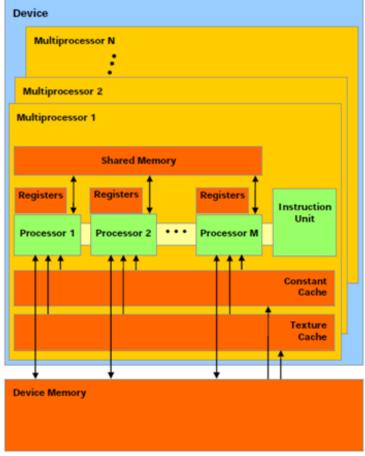

#### 1.3.2 Tilera

Tilera is a company that offers a wide range of many-core systems. These systems can have 36,64 or 100 cores. Each of the cores can execute OS-like threads and the executed threads may be totally unrelated. This system is meant for executing many sequential threads concurrently. With each core able to execute its own copy of the operating system, the core can be used in servers that handle numerous independent applications. Alternatively, one core runs a full OS while others run a "degenerate" version, making the core more efficient for single-application parallelization.

Some of the architectural highlights of the system are:

- Private caches for each of the cores.

- NUMA hierarchy.

- Fast and wide buses for the memory.

- Thread dispatching to the cores can take several hundred cycles.

- For TLR36480BG-7C<sup>1</sup>

- o 64 cores (tiles).

- $\circ$  5.6*MB* on chip cache.

- Systems frequency is 700MHz.

- $\circ$  Power consumption is approximately 23W

<sup>&</sup>lt;sup>1</sup> Taken from Tilera website

Figure 2 - Tilera'a "TILE" many core system. Image taken from Tilera.

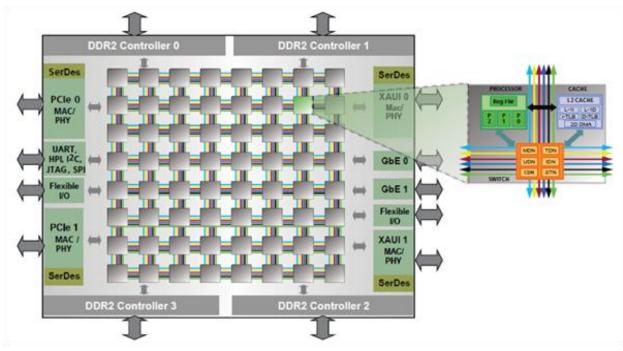

# 1.3.3 XMT

XMT, Explicit Multi Threading, is many core system that was developed at the University of Maryland under Prof. Uzi Vishkin and his team [1, 2]. This system is an accelerator and is not intended for executing sequential algorithms or for running an operating system.

Figure 3 - XMT Architecture. Image taken from Xingzhi Wen's thesis [1]

This architecture has the following properties:

- 64 cores. Each core has a private cache.

- NUMA hierarchy.

- C-like programming language.

- Efficient online scheduler.

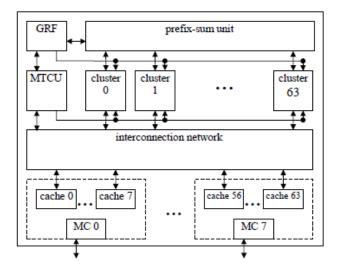

# 1.3.4 Plurality

Plurality offers a shared-memory many-core system. This system supports 32-256 identical cores with shared memory. The shared memory is both logical and physical meaning shared address space and shared physical memory, accordingly. The cores do not have private caches, thus obviating the need for cache coherency mechanisms. Same-address writes are serialized by the interconnect. The shared onchips cache is partitioned into numerous banks (with address interleaving), and a low-latency, high-bandwidth combinational multistage interconnect carries the core-cache traffic. The memory banks are equidistant from all the cores, so this is a UMA system. The absence of private caches (and a large amount of state in them) and the UMA architecture permit any core to execute any compute task with equal efficiency. This greatly simplifies programming and runtime management.

Figure 4 -Plurality's HAL architecture. Image taken from Plurality.

The shared memory offered by Plurality is 2MB - 4MB. Several memory related issues have to be dealt with:

- Memory foot print —each core uses different memory\data, to avoid thrashing, it is critical that the total amount of memory used by all the cores be smaller than the shared memory.

- Memory access pattern a bad access pattern can incur cache misses which reduce performance.

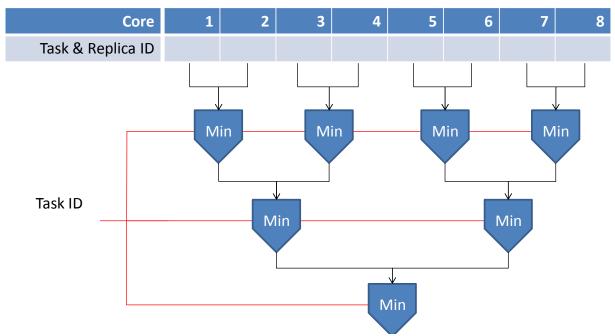

Plurality uses a task graph approach to dictate the flow of the application. This is essentially a dataflow graph at the inter-task level: a task may be dispatched once those upon which it depends have been completed.

Plurality has implemented an online hardware scheduler called the "Synchronizer\Scheduler" which is responsible for assigning tasks to cores. This hardware is also responsible for enforcing correct control flow (as expressed by the task graph). The fact that that the Synchronizer\Scheduler is online requires that is be fast in order to ensure that cores utilized as much as possible. To ensure fast scheduling, Plurality created a distributed dispatching network between the Synchronizer\Scheduler and the cores. From the moment the Synchronizer\Scheduler dispatches a task until the tasks reaches an idle core, it takes O(log(cores)) cycles. The distributed network is a tree with the root at the Synchronizer\Scheduler and the cores as the leaves. The exact number of sub-trees is dependent on the implementation. Each of

the nodes in the distributed network can complete the dispatching in one cycle, meaning that the node sends the dispatch request onwards. Plurality supports two types of dispatching:

- 1) Dispatching a single task on each sub-tree. This limits the number of dispatched task to the number of the root's sub-trees.

- 2) Dispatching a single task with numerous copies on each sub-tree. This limits the number of dispatched tasks to a given sub-tree to the total number of cores in that sub-tree. This type of dispatching will become clearer in upcoming sections, but it is worth noting that it permits the dispatching of more tasks than does the first type.

It is Plurality's goal to make this system a low power system. While exact numbers cannot be given as this platform has not been fully synthesized at the date of this publication, the numbers suggest ~4 Watts for 64 cores at 500MHz with 40nm CMOS technology. This is significantly better power-performance than x86 systems.

The Plurality architecture is extremely attractive from both power-performance, applicability and ease of programming perspectives. We therefore chose it as the primary context of our work, though much of our findings and suggestions have broader applicability.

#### 1.4 Shared-memory many-core system challenges

The progression from single core systems executing multiple threads to multi-core and many-core systems that can execute concurrent threads has raised several issues:

- Are the threads related in any way? Data? Code?

- What sort of hardware does the system have? Homogenous\heterogeneous cores? Communication methods? Memory architecture?

- How is work dispatched to the cores? What are the relations between the different tasks in the system? What programming language is used to describe the relations?

- Can the work be divided in a fashion that supplies equal work to all idle cores? How fine grain may the level of parallelism be?

- What scheduling policy should be used? What are the priorities of the tasks?

# 1.5 Performance evaluation for many-core systems

Following Moore's Law[3], that the number of transistors in a constant sized piece of silicon will double every 18 months, it is now possible to fabricate many core systems on a single chip. Today there are several many core systems in existence, which are different from each other in at least one aspect. These systems include Plurality's HAL[4] many core system, XMT [1, 5] which is a research product from University of Maryland, Tilera's Tile and GpGpu systems by companies such as NVidia[6-8], ATI and Intel.<sup>2</sup>

According to Amdahl's Law[9], the speedup of a single core system is dependent on two parameters:

- *f* the fraction of the code that is speed up.

- *S* The speedup factor.

Thus, the speedup is written as following:

$$Speedup(f,S) = \frac{1}{(1-f) + \frac{f}{S}}.$$

(1.1)

For a many-core system such that f refers to the code that can be concurrently executed on N cores, the expression from above can be rewritten as:

<sup>&</sup>lt;sup>2</sup>The purpose and target audience of each of these systems is different and thus these systems cannot be compared in all aspects.

$$Speedup_{Parallel}(f,N) = \frac{1}{(1-f) + \frac{f}{N}}.$$

(1.2)

With the rise in the number of cores, comes the problem of having enough jobs to dispatch to the different tasks. Even for programs that are embarrassingly parallel such that the number of different tasks available is greater than the number of cores in the systems, the problem of task dispatching is not a simple one. In a shared memory system, for example, when the memory requirement of each task is considerably large, such that all the required memory cannot fit in the shared cache. Allocating more tasks than the memory can maintain will cause memory thrashing and can cause performance loss compared to the situation wherein only some of the cores are working but there is no thrashing.

For systems in which each core has a cache of its own, cache coherency protocols are required in order to keep the data coherent. These protocols require dedicated hardware and usually reduce performance due to the time needed to execute the protocols.

The granularity of the work can also become an important factor in the execution time of a program. Some systems require thousands of clock cycles to dispatch a task for execution, rendering fine-grain parallelism ineffective and even damaging.

These scenarios cannot be seen directly in Amdahl's Law (1.2), however, in work done by [5, 10-12], in which Amdahl's Law is re-evaluated for parallel systems such that a performance model is created, it can be seen that an increase in the number of cores does not offer linear speedup as core performance is dependent on the core's size.

Furthermore, as each of these platforms is made by a different company there are no standard benchmarks. The programming conventions are different, resulting in code that is not easily ported. This makes comparing the different system difficult as each system optimizes each own benchmarks.

#### 1.6 Scheduling

Theoretical work on scheduling appeared long before many core systems were practical. In [13], Ullman shows that even some of what seem the simplest scheduling problems are intractable NPC (Non-Polynomial Complete). In [14], Graham shows some of the scheduling anomalies that occur when different parameters of the scheduling policy/algorithm are changed. As there is usually a relationship between the tasks in a program it is necessary to have a partial order between the tasks. Partial order scheduling has been part of many research papers in the field of scheduling [13, 15-24]. The use of partial order has spawned the creation of graphs where the partial order between 2 elements can be seen as an edge in the graph. Scheduling of these graphs has been the topic of much research as well [16-21, 23-29].

In the following subsection, a brief overview is given on scheduling and scheduling parameters. While many of these parameters are significant for offline scheduling, scheduling that is done before execution of the program, these parameters are less significant, if at all, for online scheduling where the number of steps that the scheduler can take has to be minimized to increase performance.

Ullman[13] showed that finding an optimal schedule is NP-Complete even in some of the more restricted cases where :

- 1) All tasks in the schedule are of equal length(i.e. require one time unit)

- 2) All tasks require one or two time units and there are exactly 2 cores for executing the tasks.

Despite the intractable results shown in [13], it does not mean that all scheduling problems are *NPC* In order to achieve polynomial time, some of the restrictions must be relaxed. The following properties that will be presented are attributes that a scheduling policy can take into account. When a certain attribute is known ahead of time, it is possible to relax that attribute in the scheduling policy and simplify the process. The restrictions presented here are only are a subset of the full taxonomy as it is presented in [28]. Before the taxonomy is presented, an important assumption is presented — it is assumed that each core can process no more than one task at a given time. Here are the restrictions/relaxations:

- Task information refers to the data that is known about the task as it will appear in the system:

- o Time that it will take to complete the task. <sup>3</sup>

- A start time which refers to the time that the task becomes runnable for execution.

- o A due time which is a time that by which the task should be completed.

- Machine data refers to the data concerning the cores and resources that are used in the system:

- Number of cores in the system.

- Types of cores in the system. The type of resources in the system is important as allocating the right task to the right machine becomes important when different cores work at different speeds.

- Communication Cost refers to the time that is needed to transfer data or messages of one task to another task. In various scheduling algorithms, it is assumed that if 2 tasks are assigned to the same machine (one after the other) the cost of communication between the two is considered to be zero. Communication cost, is dependent on the architecture of the system (i.e., cache, memory, interconnect).

<sup>&</sup>lt;sup>3</sup> In the original paper, a single task can have more than one execution time, where each of the execution times refers to the execution time on a specific machine.

- Task characteristics gives information on the way the tasks are related and on what will occur during the execution of the task.

- Preemption refers to if a task can be stopped in the middle of its execution and later continued.

- Equal task length are all the tasks of equal length or do the tasks have arbitrary lengths? If all the tasks are equal length, then it is easier to differentiate 2 tasks by its other properties.

- Precedence relation refers to a partial order between different tasks. It is also possible that there be no precedence relation between tasks.

- Optimality criteria refers to the problem the scheduling algorithm is trying to optimize. There are several types of minimizations criterions that can be of interest.

As can be seen from the above there are many combinations for the types of schedules that can be created by relaxing one condition or more. By adding a restriction, for example all tasks are equal length, the problem becomes less generic and it is possible to create a polynomial schedule algorithm for a specific subset of problems. Still, for many combinations of the above restrictions, the problem of finding an optimal solution is intractable. For a comprehensive work on a large set of scheduling problems it is advisable to see Brucker [27].

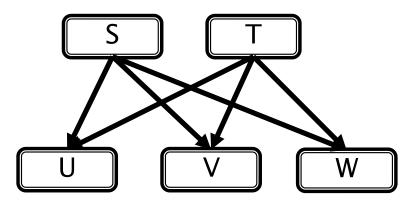

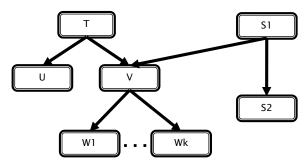

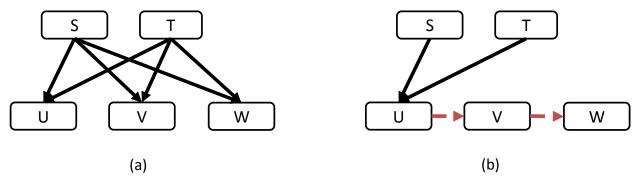

Figure 5 - An example task graph. S, T must precede U, V, W in order of dispatch and U, V, W can not be dispatched until both S, T have completed.

# 1.7 Online Vs. Offline scheduling

There are many differences between offline scheduling (a.k.a. static scheduling) and online scheduling. As the online scheduling schemes work at real time, they are required to make decisions at a quicker pace than offline scheduling schemes. Offline scheme can take their time and schedule a task to a certain core as it has time to scan the system and find the best match. These operations are time consuming and cannot be done in real-time, as doing them postpones the task dispatching. Online scheduling schemes usually do not have access to the same information that the offline scheduling schemes have access to. As such, online scheduling will give less efficient schedules than offline scheduling.

#### 1.8 Overview

In this section an introduction to shared memory and many-cores was given. Also, some of the challenges of application creation for such systems were presented along with a short introduction on scheduling. This paper deals with adding new scheduling directives that allow for an application designer to better control the scheduling of the application. These directives must be simple for an online scheduler to enforce, as scheduling must be efficient. This paper does not deal with scheduling policies, but rather with the directives that should be enforced by scheduling policies or used by scheduling policies for enforcement.

This remainder of paper is organized as follows. In Section 2, we will describe how it is possible to create workloads that can utilize all the cores, these workloads are called "duplicable tasks". Also, it will be shown that by using the current scheduling directives is not possible to express a desired ordering of tasks. In Section 3, a new scheduling directive for regular tasks will be presented. Afterwards, the different directives are compared according to their functionality and expressive power. In Section 4, scheduling directives for "duplicable tasks" will be presented. This section will start off by explaining the limitation of regular tasks and the duplicable tasks respectively. It will then be shown how it is possible to enjoy the pros of regular and duplicable tasks by creating new type of scheduling directives. The implementation of these new directives is low power and fast. We will show these directives can be implemented on Plurality like systems. Some of these directives require additional hardware. We will present this hardware and show it is low power, small in size and fast. In Section 5, an observation on inefficient use of caches for shared memory systems will be presented. This inefficiency can cause a reduction in performance of 25%. In Section 6, our conclusions will be presented as well open problems that we believe still need to be solved.

# 2 Fine grain parallelism for many-core systems

#### 2.1 Introduction

With the increase in the number of cores a system has, comes the problems of creating enough work for all the cores. At first glance, creating the work does not seem like a serious problem; however, there are many issues that need to be taken into account to achieve high utilization of the system. These are a few of the issues that need to be taken into account:

- What is the level of granularity that is desired?

- Can an algorithm be designed in a fashion in that it can be executed in parallel?

- What are the practical implications of the system executing the algorithm on the algorithm itself?

- Are there atomic instructions implemented in the system?

- O What sort of memory architecture does the system have?

- O What is the size of the memory?

- o How long does it take to dispatch work to an idle core?

- o Will it be possible to utilize all the cores of the system?

- O Does the system support preemption of tasks?

Algorithms in theory might be efficient and show a theoretical linear speedup in the number of the cores. In actuality, the speedup might be as low as 25% of the theoretical result. Explanations for this difference might be:

- Improper load balancing division of the work is not uniform amongst the cores.

- Bad memory access patterns can cause thrashing in different levels of the memory architecture.

- Overhead added to the algorithm in the transition from a serial execution to a parallel execution.

- Scheduling overhead and slow dispatching time for different tasks. Especially problematic when dispatching time is longer than execution time of task.

- Inability to adapt the parallel algorithm parameters to suit the hardware platform. For some of

the more interesting anomalies due to change in parameters of the hardware or precedence

constraints, Graham [14].

#### 2.2 Workload breakdown

Parallelizing a serial algorithm is usually not trivial. Many considerations need to be made and sometimes algorithm simply cannot be parallelized, while others can be parallelized trivially. Algorithms

that can be parallelized trivially are known as embarrassingly parallel problems. In general, parallelization of an algorithm means that workload of an algorithm can be divided into smaller units that compute different parts of the serial algorithm where each of the parts is unrelated (works on different data) and can be executed concurrently with the other parts. The following example shows how a "Matrix Multiplication" is parallelized.

Given matrices  $A_{256\times256}$ ,  $B_{256\times256}$ ,  $C_{256\times256}$  the algorithm computes  $C=A\cdot B$ :

$$A_{i,j}, B_{j,k}, C_{i,j} \quad i, j, k \in \{1..256\}$$

$row \in \{1, 2, ..., 256\}$

$$i = row$$

$$for \ j = 1 to \ 256$$

$$for \ k = 1 to \ 256$$

$$for \ k = 1 to \ 256$$

$$C_{i,j} + = A_{i,k} \cdot B_{k,j}$$

$$C_{i,j} + = A_{i,k} \cdot B_{k,j}$$

$$(b)$$

Algorithm 1 - Matrix Multiplication. (a) Presents the serial algorithm for matrix multiplication. (b) Presents the parallel algorithm for matrix multiplication

In Algorithm 1 (a), the well known algorithm for matrix multiplication is presented. This algorithm is executed sequentially on a single core. In (b), the workload of the matrix multiplication is divided into tasks, such that each task is responsible for calculating the result of a whole row in the result matrix. Since each row is computed independently of each other, it is possible to execute the different row computations concurrently.

Based on the idea that a workload is divided into smaller tasks, that each task executes the same code on different data is an efficient and simple way to implement parallel algorithms. This idea is called data parallelism and has led the development of architectures, such as NVidia's CUDA, UMD's XMT and Plurality's HAL systems. In NVidia's CUDA this is called SPMD (Single Program Multiple Data) and the tasks are called Kernels, XMT calls this idea Spawning, Plurality calls this a Duplicable task. The names are different, as are the implementations; however, the fundamental concept is the same, divide the workload of an algorithm so that the cores executes the same code on different data.

# 2.3 Forks and Joins

In the previous section, it was shown how a big task is broken into smaller tasks. In a serial program/algorithm, the single task that is responsible for executing an algorithm becomes runnable at a given time. From a parallel program's point of view, all the corresponding subtasks become runnable at exactly the same time. At this time, all the different sub-tasks can be executed in any order or

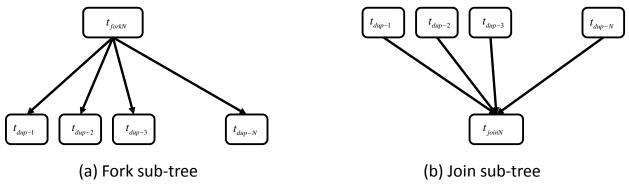

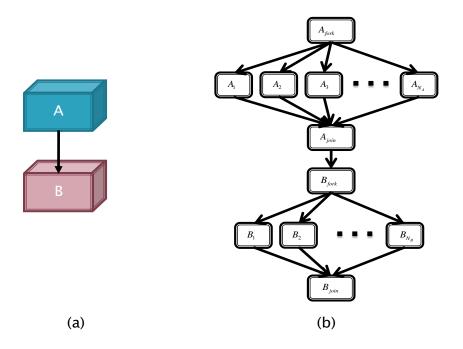

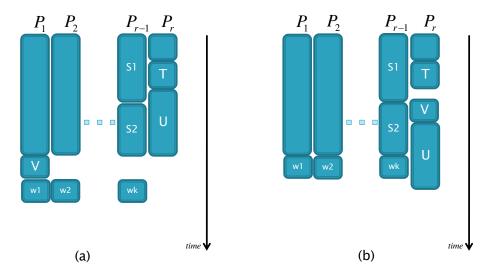

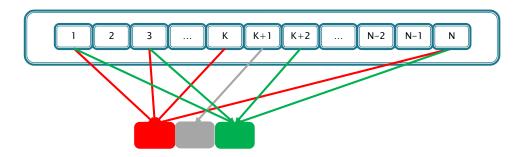

concurrently. For the matrix multiplication example, all the rows can begin execution at the same time and the order that the rows are computed is irrelevant given more rows than cores. This operation is depicted as a fork operation that releases all the tasks at the same time and thus it is the scheduler's responsibility to decide which task is dispatched first. In Figure 6 the fork sub-tree is depicted.

Figure 6 - Fork and Join sub-trees

In a serial program it is obvious when the serial part has completed as the code reaches an "end". In a parallel program the work is divided to different cores, thus, the finishing point is not as obvious. It is therefore necessary to have a synchronization point which is a blocking command that ensures that all the sub tasks have completed before moving on to the next task. This is the join sub-tree (Figure 6). By using both a fork and join on tasks that executes the same code on different data it is possible to create a "duplicable task".

#### 2.4 Duplicable Tasks

In the previous sub-sections the idea of duplicable tasks was presented. Basically these are tasks that can be divided into smaller tasks that each of these smaller tasks executes the same code on different data. These smaller tasks are called replicas. In essence, a duplicable task is made up of an algorithm (code) that each of the replicas executes and a number that states how many replicas need to be executed. As we are using Plurality's programming model which defines a duplicable task we also consider their hardware and the duplicable task implementation. In hardware, there are 2 additional fields that are maintained for a duplicable task: the number of replicas that have been dispatched and the number of replicas that have completed. The difference between these two fields gives the number of active replicas. The pros and the cons of duplicable tasks relative to conventional ones are as follows.

#### Pros:

• Changing the number of replicas in the task graph is simple. All that needs to be done is to change the number of replicas parameter for that task.

- Task graphs that contain large number of nodes/tasks can be created by using duplicable tasks because of the ease of definition of a duplicable task.

- Task maps are more readable and easier to understand.

- It is possible to efficiently dispatch duplicable tasks to idle cores (this will be shown).

- Larger task graphs become easier to design.

#### Cons:

- Scheduling-related expressive power is lost because all the replicas of the task are dependent on the fork and the join is dependent on all the replicas of the task:

- All the replicas must wait on the fork before they can begin execution.

- The task/s following the join must wait for all the replicas to complete before they can begin execution.

- The completion of the replicas is out of order. Causes for this include replicas of different lengths (data dependent) as well as non-deterministic memory access time (cache misses).

- Architecture dependency Optimizations done to a specific graph will most likely be system dependent, and changing systems may even render them damaging [14].

The focus of this work is to try and overcome the scheduling limitations of duplicable tasks while retaining the simplicity brought about by them. This research focuses on how to improve the expressive power that will be given to the task graph designer. This will be done by presenting new scheduling directives that we believe to be useful for designing task graphs and allow the task graph designer to insert what he/she believes to be crucial input to the runtime scheduler. Also, the practicality of implementing them will be considered.

# 2.5 Expressive power limitations due to precedence constraints

In this subsection, several examples will be given that show that using only precedence constraints is not enough to express the needs and desires of a task graph designer. In subsequent sections, several new scheduling directives will be presented that help overcome these problems. The first of these examples will show the limitation of precedence constraints between regular tasks. The second example will show how precedence limits the relationships between duplicable tasks.

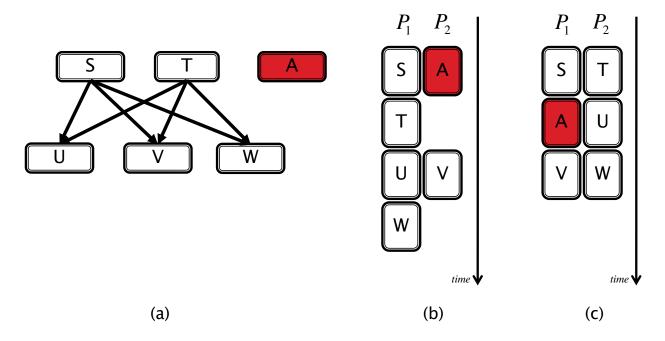

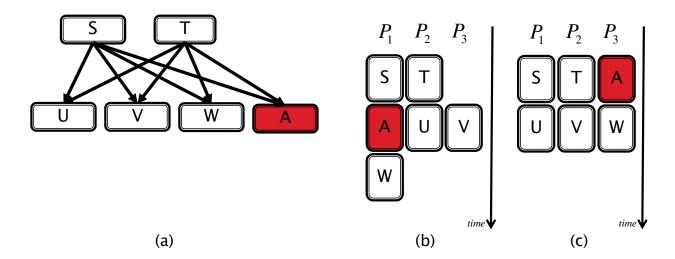

# 2.5.1 Example of limited expressive power - regular tasks

The first of these examples is depicted in Figure 7 - Example that precedence is insufficient even for same length tasks. (b) & (c) both depict schedules.(a) where the schedule can initially select S, T or A to dispatch to an idle core. Given a two-core system, it is possible to select two of these three tasks. In (b), S and A are selected prior to T. While in (c), S and T are selected prior to A. The execution time of (c) is smaller than that of (b) because U, V and W can be executed concurrently to A and cannot be executed concurrently with T. So the question that is raised, can adding a prerequisite between (S, A)

and (T,A) (in Figure 8) help fix this problem? The answer to this is equivocal. On the one hand, given the two-core system, it is possible to enforce the desired schedule. On the other hand, using the new graph on a three-core system (graphs are created offline, this can be thought of a compilation operation), then a penalty in the execution is incurred compared to an optimal scheduling of the original graph on the new system.

Figure 7 - Example that precedence is insufficient even for same length tasks. (b) & (c) both depict schedules.

Figure 8 - Updated graph with additional precedence constraints. (a) *S* and *T* precedes *A*. In (b) the graph from (a) is scheduled on a new system that has an additional core. (c) Scheduling of the original graph on the new system.

This leads to the conclusion that precedence constraints can limit expressive power.

# 2.5.2 Example of limited expressive power - duplicable tasks

The use of precedence constraints for duplicable tasks has two major implications:

- 1) All the replicas become runnable at exactly the same time, when all the prerequisites of the duplicable task have completed.

- 2) A duplicable task is considered completed only after the last of the replicas completes.

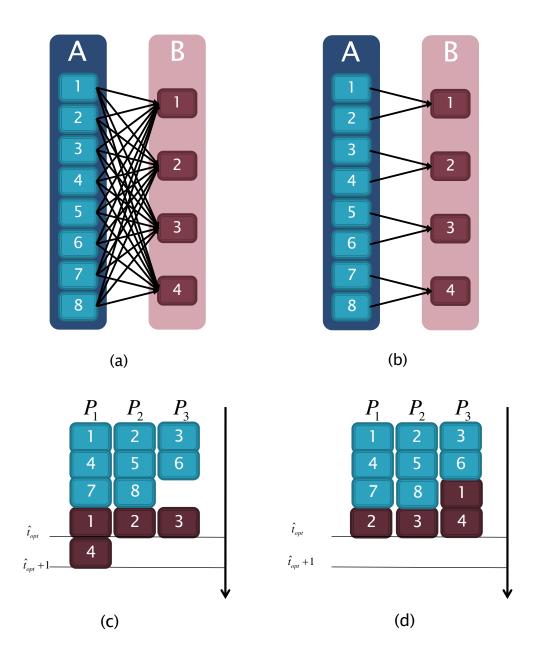

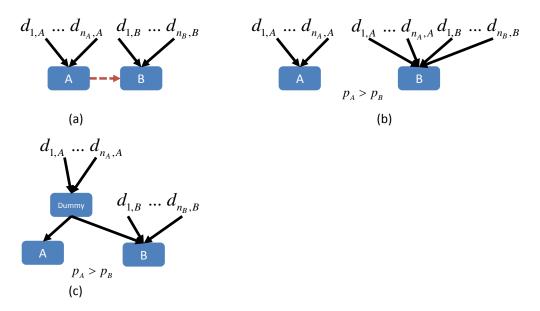

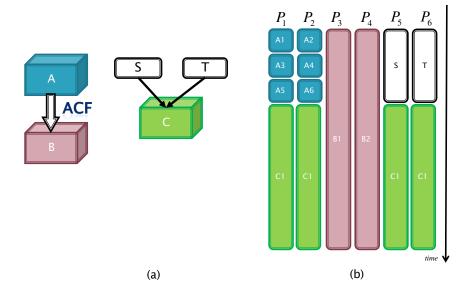

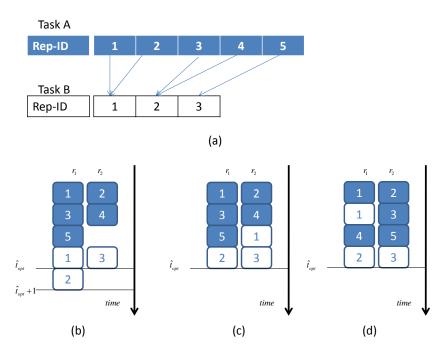

These implications are depicted in Figure 9. Each of these implications has its pros and its cons. While these pros and cons are important<sup>4</sup>, the following will only show the expressive limitations precedence constraints w.r.t. to duplicable tasks. Given two duplicable tasks A, B such that A precedes B. According to the second implication, each replica of B is dependent on the completion of all the replicas of A, in essence this Figure 10 (a). While in actuality the task graph designer may know of a finer grain relationship such as the one presented in Figure 10 (b). Scheduling the graph in Figure 10 (a) will require that all of A's replicas complete, Figure 10 (c). Scheduling Figure 10 (b) (if it were possible to express the desired relationship), would result in a shorter execution time, Figure 10 (d). In the following section we will show that it is possible to express such a relationship.

<sup>&</sup>lt;sup>4</sup> The pros and cons will be further elaborated upon in future sections.

Figure 9 - (a) A and B are duplicable tasks. A precedes B. (b) Equivalent graph to the one presented in (a).

Figure 10 - Example of limited expressive power when using duplicable tasks. Using duplicable tasks adds precedence constraints that don't exist (due to duplicable task syntax). (a) A, B duplicable tasks. A precedes B. (b) A, B duplicable tasks with a new relationship (directive) between the replicas of B and A. (c) Gantt graph of (a), assuming equal length tasks. (d) Gantt graph of (b), assuming equal length tasks.

# 2.6 Duplicable-task scheduling

Scheduling duplicable tasks is a tougher problem than it may seem at first glance. Given a task t that has N replicas, any random permutation of the N replicas is a legitimate ordering of the replicas. Scheduling a random permutation of the replicas can have implications on the execution length. Also, randomization can slow the scheduling down as a history of which replicas have been dispatched and which haven't needs to be maintained and updated. The following presents some of the problems related to scheduling of duplicable tasks:

- Data dependant replicas there are cases where the execution length of the replicas are data dependent. A special instance of this problem is when the longest replica is dispatched last, thus, increasing the schedule length of the duplicable task.

- Shared memory when the memory of the system is shared by all the cores and its size is limited, an irregular ordering of the task might cause an increase in memory misses in the shared memory (cache) due to lack of data locality which hurts the performance.

- Optimality if the scheduler used is based on a random algorithm, it is unlikely that the optimal schedule will be reached.

- Join synchronization point the join of the replicas becomes a bottleneck on the releasing of other tasks.

A result of the aforementioned reasons makes scheduling the replicas from the lowest ID to the highest ID a good and simple approach. This approach allows for quick scheduling of the duplicable tasks as the order of dispatching "inside" the duplicable task is both deterministic, simple and "chunks" of replicas can be allocated efficiently. System's like Plurality's encourages scheduling duplicable tasks in sequential fashion as this increases the number of tasks that can be dispatched in every cycle.

#### **Important Assumption**

As of this section, it will be assumed that scheduling of the replicas of a single duplicable task is done in a sequential fashion, from the replica with the lowest ID to the replicas with the highest ID.

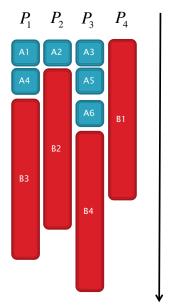

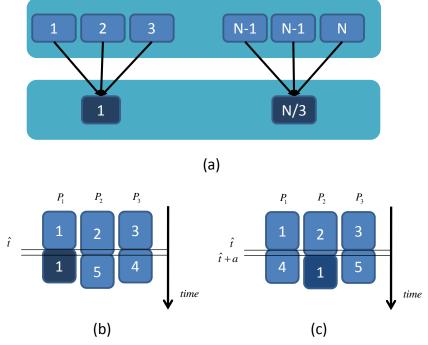

# 2.7 Different levels of granularity for duplicable tasks

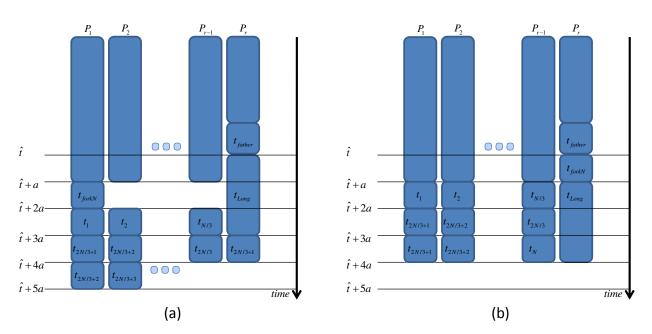

In this section the concept of duplicable tasks was presented, as were some of the pros and the cons of duplicable tasks. Another type of task was presented as well - regular task. It might be inferred that these are the only two types of task that can be used when creating a task graph. However, it is possible to get a third level of granularity that is in between the two and that is to create several duplicable tasks that execute the same algorithm on different data by dividing the duplicable task into smaller duplicable tasks that each new duplicable tasks has fewer replicas than the original. This might be seen as

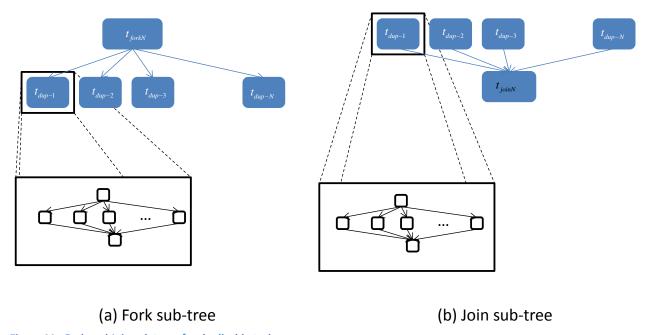

duplicable task of duplicable tasks, that is, a fork that releases a set of duplicable tasks and a join that waits on the completion of all the duplicable tasks. Although the difference between Figure 6 and Figure 11 does not seem great, the difference is that each of the tasks in Figure 11 is a duplicable task, so each of the tasks is made up of a fork and a join while in Figure 6 each task is a regular task. Also, notice that new graph does not have a join that follows all the smaller duplicable tasks. This join is optional.

By using this new type of granularity, which is between coarse grain (regular tasks) and super fine grain (duplicable tasks), it is possible to express new types of relations between duplicable tasks. Some of these relationships allow better expressing of the needs and the needs of the task graph designer. For example, each of these smaller duplicable tasks is a perquisite to another task, each of these following tasks can be dispatched upon the completion of the smaller task rather than waiting for the completion of all the replicas.

Figure 11 - Fork and Join sub trees for duplicable tasks.

We will show that there is a way to achieve a similar level of granularity without actually breaking the duplicable tasks into smaller duplicable tasks. In section 4 of this paper a way to achieve this finer grain of duplicable tasks will be presented, but, without paying the penalties of regular tasks and duplicable tasks. Beforehand, scheduling directives for regular tasks will be presented.

# 3 Scheduling directives for regular tasks

#### 3.1 Introduction

In 1.6 the concept of scheduling based on graphs was first presented. This concept has been the topic of much research. Many of these approaches use the list scheduling approach [15, 16, 18, 24, 26]. In list scheduling each node is assigned a priority and a list is created by sorting the tasks according to their priorities. It is common practice to sort the tasks from the highest priority (head of list) to the lowest priorities (tail of list). Once the list has been sorted, the following repetitive algorithm is used to schedule the list:

- 1) Select (and remove) task from beginning of list. Task with highest priority is selected.

- 2) Select runnable resource to execute task.

These two stages are repeated until list is empty.

The criteria on which the priorities of the tasks are decided, is called the scheduling policy. The scheduling policies should try to optimize some performance measure while enforcing correctness (precedence constraints). The problems that arise from using these algorithms is that task graph designer does not have a straight-forward ability to state which of task is considered more important as priorities are not designated in the task graphs but rather by the scheduling policy.

It should be noted that priorities do not override precedence, but rather help select a task from the list of runnable tasks based on its level of importance. Priorities can be a useful tool in the hands of a task graph designer as the designer is aware of algorithm constraints and the optimization criteria(which may not be one of criterias as presented in [30]). Also, each of the tasks receives a unique priority. In this paper, it will be assumed that the priority is given by the task graph designer (i.e. offline), though this priority can also be given by a scheduling policy, and the priority will be enforced online by selecting the task with the highest priority from the list of runnable tasks.

#### 3.2 Start After Start

In this section a new scheduling directive for regular tasks will be presented. This directive is known as Start After Start, SAS for short. Earlier in this paper, an example was shown that precedence constraints are not enough for expressing everything that is desired. Precedence states, that a task is not runnable for execution until all of its prerequisites have completed. What if all that is required is that the same task only wait until all these so called "prerequisites" have been dispatched? This cannot be expressed simply using precedence. It is the goal of SAS to achieve this. This section starts off by presenting motivation for this directive, after which an implementation of this directive is shown.

#### 3.2.1 Motivation for Start After Start

#### Example 1: Insufficiency of precedence

Consider the graph in Figure 12, where:  $p_v > p_u$  and w(v) < w(u). From the graph in Figure 12, it is depicted that U depends only on T, while V depends on  $V, S_1$ . When T completes, U is runnable for execution. If  $S_1$  has yet to complete, U will be dispatched. This will result in the schedule depicted in Figure 13 (a). However, if U can be blocked until the dispatching of V, even leaving a core idle for a while, it is possible to improve the execution time as depicted in (b). Blocking U until V has been dispatched is exactly SAS.

Figure 12 - Motivational example for SAS

Figure 13 – Scheduling of a task graph where priority and precedence is not enough to achieve optimal execution time. (a) U is dispatched before V. (b) SAS is used. U is blocked from execution until the dispatching of V. Execution time of (b) is better than the execution time of (a).

Example 2: Reducing number of edges in graph.

Consider graph (a) in Figure 14 where S,T are prerequisites for U,V,W such that  $p_u>p_v>p_w$ . A corresponding graph is depicted in (b), where V can not start until U starts and W can not start until V starts. V cannot be dispatched until all of U's prerequisites have completed which are also V's prerequisites. The difference between the graphs, is that the graph in (b) enforces a dispatch order.

Figure 14 - Two equal task graphs (a) Graph based only precedence. (b) Graph based on precedence and SAS.

#### 3.2.2 Implementation of SAS directive

Implementing this primitive can be done using only precedence constraints and using priority, it is not possible to implement this primitive without one of them:

- Without using priorities it is not possible to state which of the tasks is more important than the other and so the scheduler can decide which of the tasks to dispatch.

- Without using precedence constraints, as soon as one of the tasks is runnable the scheduler can schedule it and as will be shown, a common dependency is required.

By adding a unique priority level to each task it, it is possible to implement this construct. In Figure 15, two implementations show how to implement the SAS primitive:

Figure 15 - SAS Implementation (a) Desired graph (b) First implementation, adding A's precedences to B. (c) Adding a dummy task that receives all of A's precedence. B is dependent on Dummy as well.

It is should be noted that  $p_A > p_b$ . Without this knowledge in both (b) and (c) of Figure 15, if A and B are both runnable, they are both viable options by the scheduler. The implementation of this primitive is based on adding A's dependencies to the already existing dependencies B has. This will ensure that B does not become runnable at least until A does . The addition of the priority, ensures that A will be dispatched before B if both are runnable.

|                                                                                        | First implementation (b) | Second Implementation (c) |

|----------------------------------------------------------------------------------------|--------------------------|---------------------------|

| Edges Added                                                                            | $n_A$                    | 2                         |

| Vertices Added                                                                         | 0                        | 1                         |

| During scheduling: How many additional updates are needed when completing a task $A$ ? | $n_A$                    | 2                         |

**Table 1 - Comparing SAS implementations**

From Table 1 it is possible to see that the second solution is cheaper in memory as it uses as fewer edges<sup>5</sup> and during the scheduling, only Dummy needs to be informed of its preceding rather than A and B in the first implementation.

<sup>&</sup>lt;sup>5</sup>It is necessary to compare the memory size of a vertex to that of an edge to be certain which of the approaches is cheaper in memory.

# 3.3 Regular tasks scheduling directives summary

In summary, three types of scheduling between regular tasks were seen. The following will present these directives according to their expressive ability, from the strongest to the weakest:

- 1) Start After Complete this is another name for precedence constraints which states that certain tasks cannot be dispatched until all their prerequisites have been completed.

- 2) Start After Start certain tasks cannot be dispatched until other tasks have been dispatched before them, even if a core remains idle as a result.

- 3) Priority allows selecting a task from a set of tasks that can be dispatched.

# 4 Scheduling directives for duplicable tasks

# 4.1 What are scheduling directive for duplicable tasks?

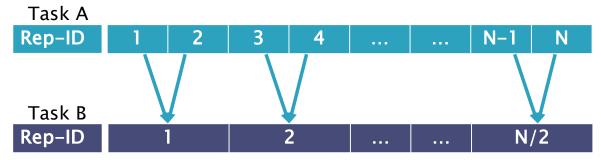

A scheduling directive, for duplicable tasks can be thought of as a special relationship between replicas of two or more duplicable tasks such that replicas are no longer dependant on the completion of all the replicas of another duplicable task. For example, the i-th replica of B is dependent on the  $2 \cdot i$  and  $(2 \cdot i + 1)$  replicas of task A. In other words, it is possible to dispatch  $B_i$  after  $A_{2 \cdot i}$  and  $A_{2 \cdot i + 1}$  have completed(such a relationship might be useful for Merge-Sort[31] or parallel addition of a vector ). An example of this was shown earlier in section 2.5.2 (Figure 10) and another example is given here as well Figure 16.

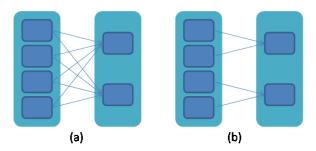

Figure 16 - Two duplicable tasks and their dependencies. (a) Merge-Sort implemented by duplicable tasks (b) A desired Merge-Sort implementation by duplicable tasks.

There are other considerations (not including, specific replicas becoming runnable earlier) that make scheduling directives desirable. These include, placing expressive power in the task graph designer hands so that he can create a more accurate task graph due to the finer-grain granularity given to him. The benefits and requirements of each directive will be discussed in the sub-section of the directive. There are certain constraints on the new directives:

- Efficiency dispatch numerous replicas in a small number of decision steps like duplicable tasks.

- Fast currently dispatching a replica takes  $O(\log(Core))$  requires a small number of cycles. Thus, it is desirable to stay with-in this time limitation and so the new directives should try and support this limitation as well.

- Low power As the system that we are using is a Plurality-like system, there is a power constraint that needs to be meet. Any new hardware that is implemented for such a system should be low power.

Before presenting the new directives, consider the following example, given A, B duplicable tasks. Both A and B access the same data array X using the same access pattern<sup>6</sup>. X is exactly twice the size of the shared memory . If all of A is executed prior to any of B's replicas, then the shared memory will first contain the first half of X and then this will be removed and the second half of X will be fetched. As B has the same access pattern, this will happen also for B. Both tasks will suffer from the cache misses. Rather than executing B after A, by executing B's replicas concurrently(not necessarily simultaneously) to A's in a way that A cannot advance enough to clear the cache, it will be possible for B to use data that has already been fetched(following A's cache misses) and that is in cache. In this example, we see a speedup that is a result of the reduction in the number of cache misses. While this idea offers a speedup due to a decrease in the number of cache misses, we will see that this idea is also parameter dependent.

In following subsections we will present directives which we have found to be interesting. While there are many interesting relationships, some are impractical as they do not allow holding up the constraints that were presented. Consider relationships that are sporadic or semi-sporadic which means that it is hard to define a regular relationship between the replicas of the duplicable tasks, such as the one depicted in Figure 17 . For such scenarios, it might not even be worthwhile to define a relationship as the overhead or implementation might be expensive. In this paper we not deal with such random relationships.

Figure 17 - Sporadic relationship

At first glance, there seem to be several obvious workarounds for creating duplicable task relations. These include using regular tasks instead of duplicable and the fusion of two duplicable tasks into one. While each of these workarounds offers a solution to the desired problem, they create new problems that need to be dealt with. In the following two sub-sections, these workarounds will be reviewed and it will be explained why they are not the desired solution.

.

<sup>&</sup>lt;sup>6</sup> If  $A_i$  accesses an address  $X_i$ , then  $B_i$  accesses the same address  $X_i$ .

# 4.2 Regular tasks are simply too much

An obvious question that can be raised following the previous sub-section is: Why use duplicable tasks when regular tasks can easily do the job? In essence, replace N replicas of the duplicable task with N regular tasks. This solution is not good for several reasons:

- The task graph will bloat up in size.

- Every time that application parameter changes (for example the dimensions of a matrix in a matrix multiplication operation) the number of regular tasks needs to be updated, in comparison with simply changing the number of replicas of the duplicable task.

- In actuality, the size of the graph is limited by the hardware. Increasing the size of graph is not feasible.

- Dispatching regular tasks is less efficient than the duplicable task. This is because the scheduler can dispatch several replicas of a duplicable task in a single cycle.

Following these explanations it is possible to see that switching the duplicable tasks to regular tasks simply doesn't work.

#### 4.3 Task fusion is not feasible

In this sub-section, the answer to the following question will be given: Given two duplicable tasks A, B, why not fuse these two tasks into one new duplicable task C? Task fusion seems almost like the intuitive approach to solving this problem. As the task graph designer knows the relationships between the tasks, the task graph designer redesign the graph accordingly. However, task fusion suffers from several deficiencies and problems:

- Concatenation of two functions into a single function is not desirable from a software point of view as this reduces code reusability.

- Duplicable tasks may not be the same length.

- Considerably simple relationships are problematic. For example, given that  $B_i$  is dependent on  $A_i$  and  $A_{i+2}$ , which replica of C,  $C_i$  should compute  $A_i$ ? Should  $C_i$  or  $C_{i+2}$  compute it?

- $\circ$  Each of the  $C_j$  replicas will compute  $A_i$  and  $A_{i+2}$ . This causes redundancy in operations. While this approach is still sufferable for this scenario, for cases that  $B_i$  is dependent on more values, this approach is insufferable.

- Let  $C_j$ , compute  $A_{j+2}$ . However, do to out of order completion,  $C_{j+2}$  which is dependent on  $C_j$  cannot be dispatched until the completion of  $C_j$ .

While task fusion might be suitable for some problems, it is not suitable for many.

### 4.4 What sort of directives do we want?

Earlier in this section, the need for more intricate relationships between duplicable tasks was presented. After this, two approaches to implementing the relationships were presented. While both approaches were found wanting, they approaches did not discuss what the relationships would be but rather how to implement the relationships once defined. In this sub-section, we will try and answer the question: What relationships do we want? Answering this question will help us define the new scheduling directives. We would like relationships that answer some of the following criteria:

- Correctness Can a certain order of execution be enforced when using the directive? The order

of execution must be correct for all scheduling instances and not for a single schedule. For

example, if both replicas access the same memory address, can an exact order of the replicas to

the data be enforced? Another example, if there is a dependency between replicas of the tasks,

can this dependency be enforced?

- Fairness Does the primitive allow sharing resources in a fair manner between the duplicable task? The following two are criterions interest us:

- Number of cores Do the tasks use the same number of cores? This infers to equal amount of computation time for the tasks.

- Dispatching Is it possible to dispatch replicas from both duplicable tasks such that neither of them is starved?

- Cache issues By using the directive is it possible to improve performance of the memory?

- Total memory required By using the primitives is it possible to reduce the total amount of memory required at a given time?

- Cache misses is it possible to reduce the number of cache misses required by the tasks?

- Efficient scheduling

- Can the relationship be calculated quick enough to allow for fast and efficient scheduling?

- Can scheduling work be done background (when there are no idle cores)?

Answering these questions is not simple for the general case as many of the answers here are dependent on the parameters of the application and the selected directive. It will be shown that some of the directives do not support all the criteria, while in actuality some of criteria conflict with each other. Motivational uses will be presented for each directive.

Before proceeding to the scheduling directives, the following observation on memory usage will be presented. While, at times the exact memory access pattern is not known, it is still possible to present an upper bound on the total amount of memory that is required.

**Definition:** Let  $Mem(rep_{r,A})$  be the memory used by the r-th replica of A.

Given a duplicable task A that has R replicas currently executed in the system, the upper memory bound (UMB) is:

$$UMB = \sum_{r \in R} Mem(rep_{r,A}).$$

For duplicable tasks that all the replicas have the same access pattern and use the same amount of memory, it is possible to get a closer approximation:

$$UMB_{similiar} = R \cdot Mem(rep_{r,A}).$$

There are also scenarios in which the replicas access some of the memory that other replicas access. For this scenario a tighter bound can be given:

$$UMB_{shared} = \bigcup_{r \in R} Mem(rep_{r,A}).$$

It should be noticed that all these expressions discuss the memory that is currently being used. However, this does not take into account the out of order completion such that different replicas in R may not be consecutive, in which case the expressions should be changed to support  $\hat{R}$ .  $\hat{R}$  is defined as following:

$$\hat{R} = \{r \mid \min(R) \le r \le \max(R)\}.$$

These expressions become slightly more complicated when there is more than one duplicable task involved as another memory access pattern needs to be considered. First of all there are two sets of executed replicas  $R_A$ ,  $R_B$ . Also, this access patterns needs to be considered from two angles:

- Memory usage Do the duplicable tasks use the same memory?

- Access pattern Do the duplicable tasks have similar access patterns?

Do the duplicable tasks use the same memory?

- If they use the same memory, another question needs to be answered. Do they have a similar access pattern?

- o If they do, the size of  $\widehat{R}_A$  will be defined by the number of dispatched replicas that it leads B by. This is because, eventually B will need to access this memory and it is preferable that this memory not be removed from the shared cache.

- If there is no similar access pattern, then as far as we are concerned the relationships is sporadic and this is of no interest to us.

- The tasks do not use the same memory. Do the tasks need the same cache lines at the same time? If so, this can cause memory thrashing.

## 4.5 Priority Primitive for Duplicable Tasks

Adding priority primitives to duplicate tasks is slightly more complicated than it is when used just on regular tasks. For a single duplicable task, setting priorities is easy due to in order allocation. The task with the smallest id receives the highest priority and the task with the largest priority receives the lowest priority.

Each replica has two priorities, external and internal. The external priority is the priority of the duplicable task. The internal priority is the priority that replica has over the other replicas in the duplicable task, which is basically its position (index) in the duplicable task. In essence the priority of a single replica depicted as a 2-tuple made up of the external priority and the internal priority  $(p_e, p_i)$ .

The following is based on combinations between regular and duplicable tasks:

- Given a regular task r and a duplicate task d with priorities  $p_r$  and  $p_d$  ,respectively, there are several ways to schedule the tasks,

- o  $p_r = p_{d,e}$ . As the priorities must be unique, the internal  $p_{d,i}$  priority is checked and accordingly one of the following will happen:

- All the replicas with a  $(p_{d,e}, p_{d,i})$  higher than  $p_r$  will be schedule before r. After this r will be dispatched, followed by the remaining replicas.

- r is dispatched before all the replicas of d This situation is unlikely because in actuality  $p_r > p_d$ . It would be wiser to set the priorities accordingly so that efficient dispatching will be possible.

- All the replicas of d are dispatched before r. This situation is unlikely because in actuality  $p_d > p_r$ . It would be wiser to set the priorities accordingly so that efficient dispatching will be possible.

- o  $p_r > p_d r$  is dispatched before a single replica of d is dispatched. This priority primitive is useful the task graph designer that knows that a certain regular task takes more time than each replica of d. This will allow, running several and different replicas of d on the same core while r is executed on a different core.

- o  $p_d>p_r$  only after all the replicas of d have been dispatched, can r's replicas be dispatched.

It should be noted that different priorities for r and d can change the latency of the program.

- Given two duplicable task  $d_1$  and  $d_2$  with priorities  $p_{d1}$  and  $p_{d2}$  respectively, there are several ways to schedule the tasks:

- $\circ$  Both  $d_1$  and  $d_2$  have the same priority both tasks (and their replicas) can be executed concurrently and replicas can coexist side by side and so the internal independence of

<sup>&</sup>lt;sup>7</sup> Out of this 2-tuple it is possible to create a singleton number which can be seen as the absolute priority of the replica. This allows giving each replica a unique priority.

- the duplicable tasks decide which replica is dispatched first. This resembles Start After Start, but, for duplicable tasks.

- One of the duplicable tasks has a higher priority (without the loss generality,  $p_{d1} > p_{d2}$ ), in which case all of its runnable replicas will be executed before the runnable replicas of the other duplicable tasks.

We did not deal with directives between regular tasks and duplicable tasks in this paper.

## 4.6 Applicable directives for duplicable tasks

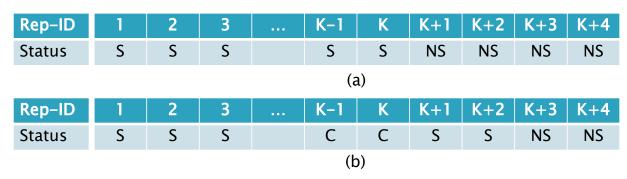

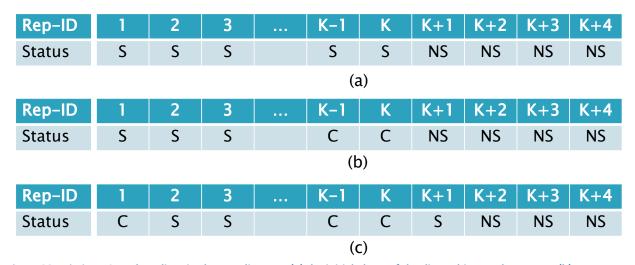

In this sub-section new scheduling directives will be presented. The scheduling directives that will be presented in this sub-section can be implemented using existing data that is kept for each duplicable task. As a quick reminder these fields are given in the following table.

| Variable         | Name | Туре | Description                     | Is currently supported |

|------------------|------|------|---------------------------------|------------------------|

| Number of        | n    | Int  | Number of replicas that need to | Yes                    |

| replicas         |      |      | be allocated.                   |                        |

| Dispatched       | S    | Int  | Counts how many replicas have   | Yes                    |

| replicas counter |      |      | been dispatched/started.        |                        |

| Completed        | С    | Int  | Counts how many replicas have   | Yes                    |

| replicas counter |      |      | completed.                      |                        |

Table 2 - Mandatory information for duplicable tasks

A duplicable task is not considered complete until c = n. Also, it is worth noting that replica allocation is done in-order from the replica with the lowest id until the replica with the highest id.

Corollary: Given a duplicable task A, A.  $s \ge A$ . c at all times. This is due to the fact that a replica can't be completed before it has been dispatched.

In the following subsection these notations will be used given a duplicable task A to state if  $A_i$  has started or completed:

- $S(A_i)$  -returns true iff  $A_i$  has started.

- $C(A_i)$  –returns true iff  $A_i$  has completed.

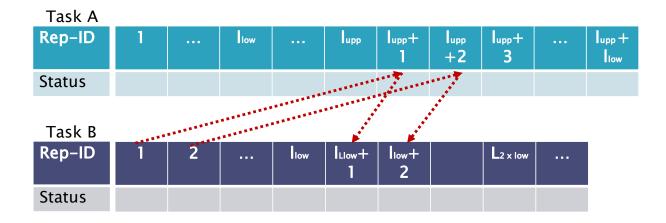

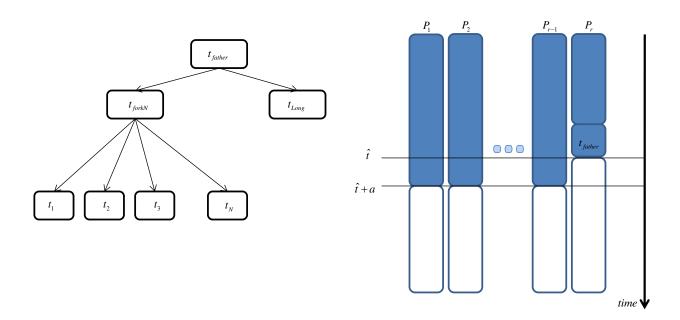

## 4.6.1 Start After Start for duplicable tasks

Start After Start, SAS for short, was introduced earlier in this paper in the context of controlling the order in which regular tasks can be dispatched. This idea comes up for duplicable tasks as well. Basically, the question that is asked, is there a way to state that certain replicas can start only after certain replicas from other task have started? The answer to this is: yes, there is a way to state that certain

replicas are dependent on the replica dispatching from a different duplicable task. Given two duplicable tasks, A and B, the replicas of B are dependent on the dispatching of A's replicas and the replicas of A are dependent on the dispatching of B's replicas. If the latter had not been stated, it would be possible to dispatch all of B's replicas without dispatching a single replica of A.

In the previous sub-section, when priorities were discussed, it was stated that each replica has a priority. It is undesirable that at each dispatch the scheduler compare priorities of the task as this will reduce efficiency. It is the job of this directive to do this. The directive suggests that A will lead in the number of replicas dispatched. Initially it might seem that all that is required is a number l that states how many more replicas of A have started before replicas of B. However, the use of a single number will cause a single degenerated scheduling as will be explained, is based on the priority level alternating between the two tasks. To overcome this problem, two numbers will be used: an upper boundary and a lower boundary.

| Name      | Туре    | Descriptions                                                                                                                                                         |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A         | Task    | The first task.                                                                                                                                                      |

| В         | Task    | The second task.                                                                                                                                                     |

| $l_{upp}$ | Integer | Maximum number of dispatched replicas which A may be ahead of $B$ .                                                                                                  |

| $l_{low}$ | Integer | Minimal number of dispatched replicas of A may be ahead of $B$ , except for the initial state until where fewer than $l_{low}$ replicas of $A$ have been dispatched. |

Table 3 - SAS parameters

#### Remark:

Recall that A has a higher priority than B. Therefore, whenever replicas of both tasks are dispatchable from a precedence constraint perspective, A's replicas will be preferred over B's as long as A leads by at most  $l_{upp}$ . If A's replicas are dispatchable and B's are not, A can lead up to  $l_{upp}$ . Similarly, if B's replicas are dispatcheable, but A leads by fewer than  $l_{low}$  than none of B's replicas will be dispatched.

To better understand the degenerated case, consider, the case when there is one boundary, l. In this case, A will dispatch l replicas before B can dispatch a single replica. After this, B can dispatch a single task without violating the terms of the directive which states that A leads by l replicas. After this, A can dispatch a single replica. This situation of alternate dispatching will repeat itself until both tasks have completed. Several downsides of this include the fact that only a single replica can be dispatched per scheduling move/decision. Because of the desire to be able to control the size of the task dispatching another parameter is needed. This parameter will be the lower boundary.

40

$<sup>^{8}</sup>$  It will be assumed that  $l_{upp} \geq l_{low} > 0$ .

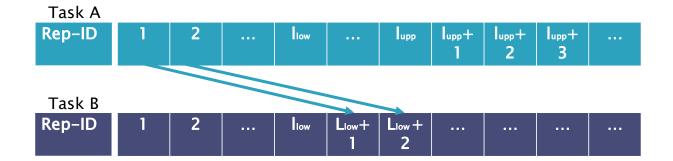

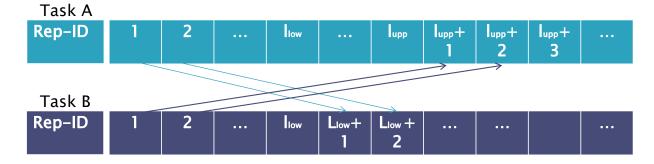

For any given duplicable task, the scheduling will be sequential (in order), which states that, for a specific replica i, i cannot be dispatched until all the (i-1) replicas prior to i have been dispatched. For task A, A cannot advance more than  $l_{upp}$  replicas than task B, due to this,  $A_i$  is dependent on the starting (dispatching) of  $B_{i-l_{upp}}$ , this is depicted in (4.1) by placing a SAS constraint from to  $B_{i-l_{upp}}$  to  $A_i$ . This ensures that the upper boundary is not violated by letting A run ahead. Task B will be behind task A by a number that is in the range  $(l_{low}, l_{upp})$ . This is done by placing a SAS constraint from  $A_{i+(l_{unn}-l_{low})}$  and  $B_i$ , this ensures that the lower boundary is not violated and that B doesn't run ahead, the formal definition of this in (4.2). Now that the two boundaries for this directive were presented, it should be noted that by selecting  $l_{upp} = l_{low} = 1$ , it is possible to recreate the situation that was described for the single parameter.

Figure 18 - SAS for duplicable tasks. The SAS edges are in both directions.

$$\begin{cases}

S(A_i) \leftarrow \left\{S(A_{i-1})\right\} & i < l_{upp} \\

S(A_i) \leftarrow \left\{S(A_{i-1}), S(B_{i-l_{upp}})\right\} & i \ge l_{upp}

\end{cases} \tag{4.1}$$

$$\begin{cases}

S(A_{i}) \leftarrow \{S(A_{i-1})\} & i < l_{upp} \\

S(A_{i}) \leftarrow \{S(A_{i-1}), S(B_{i-l_{upp}})\} & i \ge l_{upp}

\end{cases}$$

$$\begin{cases}

S(B_{j}) \leftarrow \{S(B_{j-1})\} & j < l_{low} \\

S(B_{j}) \leftarrow \{S(B_{j-1}), S(A_{j+low})\} & j \ge l_{low}

\end{cases}$$

$$(4.1)$$

What remains to do is to find an efficient expression that can compute the formal definition as is presented in (4.1) and (4.2). The following expressions do exactly this. These expressions can be easily and efficiently (power-wise) implemented in hardware, which enables fast scheduling. Replica dispatching for either of the tasks will happen only when the results of the expressions are positive.

$$alloc_A = l_{upp} - (A.s - B.s)$$

(4.3)

$$alloc_B = (A.s - B.s) - (l_{low})$$

(4.4)

A cannot advance more than  $l_{upp}$  dispatched replicas, this is seen in (4.3), where the difference in the number of dispatched, a.k.a the lead, is received from (A.s-B.s). Following this the difference between the maximal lead and the actual lead is computed.

B is limited to how close it can get "near" A. The distance between them is computed. Only if the lead is greater than  $(l_{upp} - l_{low})$ , can B dispatch replicas some of its replicas (because B can come closer to A).

Answers to the questions raised earlier in this chapter:

Correctness – It is not possible to enforce correctness using this directive as the replicas are scheduled only based on the dispatching of the other task and not the completion of the other replicas. Even by using substantial upper boundary correctness cannot be enforced as a certain replica might take an infinitely long time and thus the dependent task might begin dispatching before this replica has completed.

#### Fairness:

- Dispatching This primitive ensures fair dispatching as there is an upper limit to how many replicas one of the tasks can dispatch before replicas from the other must be dispatched before it can continue.

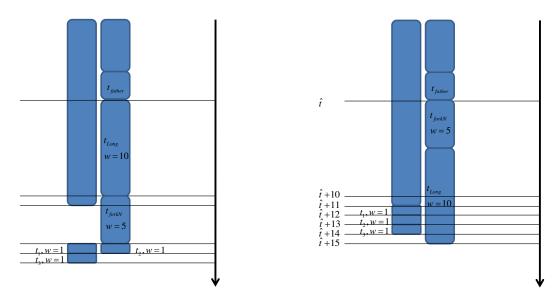

- O Number of cores This directive does not guarantee fairness in the number of cores. Consider the case where the replicas of B are considerably longer than those of A, for example  $10^4$  longer. Also, it will be assumed that there are plenty of replicas (this can be a near infinite number) for each of the tasks and the number of cores is small compared to the number of replicas. At some point in time, A will be unable to dispatch more tasks without B allocating replicas before it. At this time, every core that becomes free will receive either a replica of B or receive a replica of A followed by a replica of B. Due to the fact that the number of cores is small compared to the length of the replicas and the number of replicas, all the cores will be executing replicas of B. This is depicted in Figure 19.

Figure 19 – Example wherein task B takes over all the cores. Upper = 3. Lower=1.

#### Cache issues:

- Total memory required This answer is parameter dependent and can go either way, as was explained earlier in this chapter.

- Cache misses in general, it is possible to reduce the number of cache misses of both replicas in the case that both tasks use the same memory as was explained earlier. However, it is possible to increase the number of memory misses by causing memory thrashing. This scenario can be created for the case that the duplicable tasks access different data arrays that use the same cache lines, respectively. By using a similar access pattern to the data and dispatching replicas alternately a reduction in performance will be visible immediately.

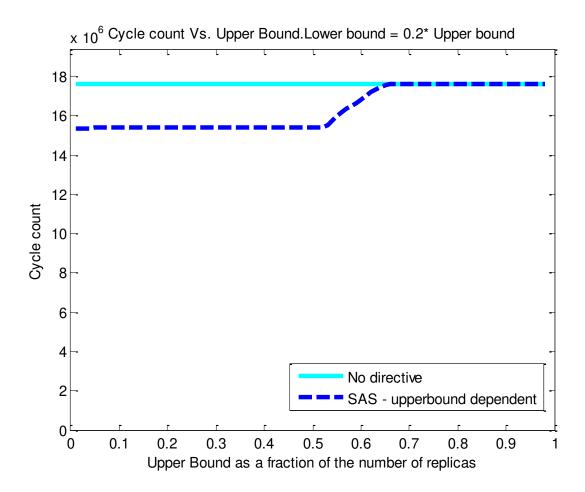

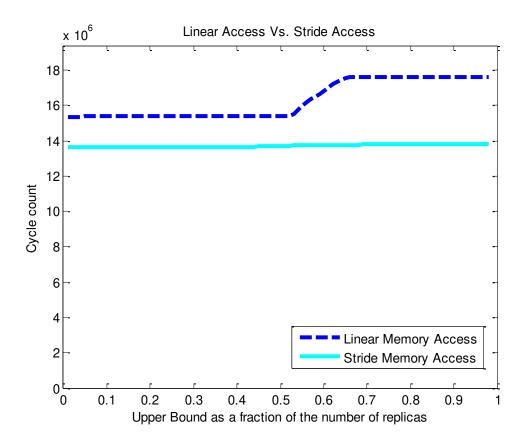

### Scheduling efficiency